3D/2.5D IC集積向けパッケージング

IC技術の進歩に伴い、より信頼性が高く効率的なパッケージングソリューションの必要性がますます高まっています。3D/2.5D ICインテグレーションの登場により、半導体パッケージングの複雑さは著しく増大しました。3D/2.5D ICインテグレーションは、複数のIC層を単一のパッケージに積み重ねる技術です。各層は、シリコン貫通ビア(TSV)とマイクロバンプを使用して接続されます。このタイプのインテグレーションは、従来の2Dパッケージングと比較して、より効率的でコスト効率の高いソリューションを提供します。しかし、3D/2.5D ICインテグレーションの複雑さには、より高度な半導体パッケージングソリューションが求められます。

3D/2.5D ICをパッケージングする場合、半導体パッケージング材料は、増大した複雑さに対応し、各層間の信頼性の高い電気的接続を提供できる必要があります。また、製造および動作中に発生する極端な温度や圧力に耐えることができなければなりません。さらに、半導体パッケージングは、層間の高密度な相互接続に対応できる必要があります。

株式会社ナノシステムズJPは、最も要求の厳しい要件を満たすために、高性能な3D/2.5D ICパッケージング製造サービスを提供しています。最高レベルの性能と信頼性を実現し、お客様が最高レベルの設計、電力、および熱効率を達成できるようにします。

標準的なプロセスフロー

シリコンウェハー内のTSV

2. 裏面加工

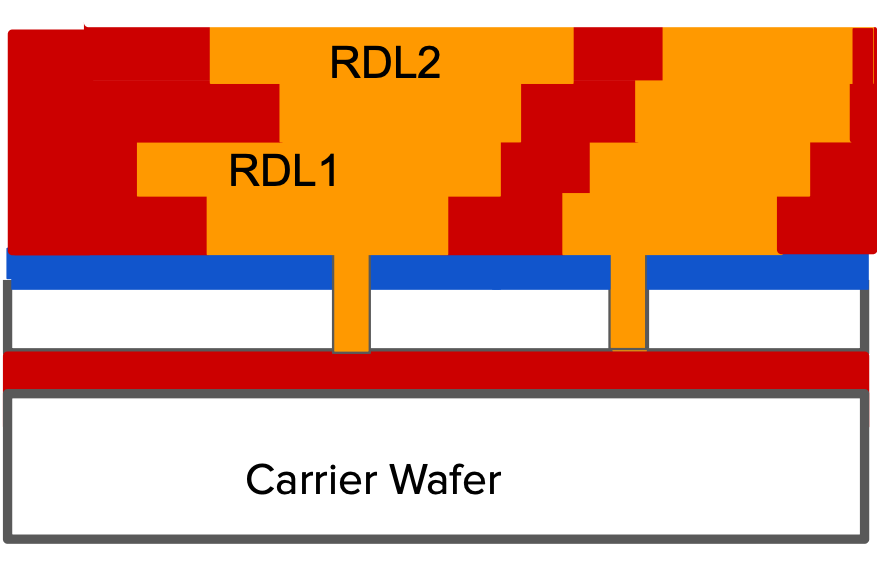

2. 裏面RDL

3.UBMおよびC4バンプ

3.表面加工

2. 表面UBMおよびCuポストまたはピラー製造

チップ|ウェハー

3. パッケージ基板

4. アンダーフィルおよびモールド

3D/2.5D IC集積化のためのパッケージング製造プロセスについてご質問がございましたら、お気軽にお問い合わせください。